# A tech talent and innovation flywheel FORGING VIET NAM'S SEMICONDUCTOR FUTURE

Public Disclosure Authorized

# 特别提醒

### 行业交流分享群

**分享**:可获取人资行业的报告、方案及其他学习资源,上新群内通知

交流: 求职、找人、找资源、找供应商

#### 免责声明

第三方声明:本报告所有内容(数据/观点/结论)整理于网络公开渠道,均不代表我司立场,我司不承担其准确性、完整性担保责任。

**侵权处理承诺**:如报告内容涉嫌侵权,请 立即联系客服微信,我司将在核实后第一 时间清理相关内容并配合处理

© 2025 International Bank for Reconstruction and Development / The World Bank 1818 H Street NW

Washington DC 20433

Telephone: 202-473-1000

Internet: www.worldbank.org

This work is a product of the staff of The World Bank with external contributions. The findings, interpretations, and conclusions expressed in this work do not necessarily reflect the views of The World Bank, its Board of Executive Directors, or the governments they represent.

The World Bank does not guarantee the accuracy, completeness, or currency of the data included in this work and does not assume responsibility for any errors, omissions, or discrepancies in the information, or liability with respect to the use of or failure to use the information, methods, processes, or conclusions set forth. The boundaries, colors, denominations, links/footnotes and other information shown in this work do not imply any judgment on the part of The World Bank concerning the legal status of any territory or the endorsement or acceptance of such boundaries. The citation of works authored by others does not mean the World Bank endorses the views expressed by those authors or the content of their works.

Nothing herein shall constitute or be construed or considered to be a limitation upon or waiver of the privileges and immunities of The World Bank, all of which are specifically reserved.

#### **Rights and Permissions**

The material in this work is subject to copyright. Because The World Bank encourages dissemination of its knowledge, this work may be reproduced, in whole or in part, for noncommercial purposes as long as full attribution to this work is given.

Any queries on rights and licenses, including subsidiary rights, should be addressed to World Bank Publications, The World Bank Group, 1818 H Street NW, Washington, DC 20433, USA; fax: 202-522-2625; e-mail: pubrights@worldbank.org.

Cover design: Ha Doan & Duong Phan

# FORGING VIET NAM'S SEMICONDUCTOR FUTURE

A tech talent and innovation flywheel

# CONTENTS

| ACRONYMS                                                                           | VI   |

|------------------------------------------------------------------------------------|------|

| ACKNOWLEDGEMENTS                                                                   | VIII |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

| 3.4. University infrastructure: capital intensity of building the talent pipeline  |      |

| 3.5. Financing and incentives for university training and innovation               |      |

| 3.6. Talent and innovation: implications for Viet Nam's value chain ungrading path | 30   |

| BOXES                                                                                                                        | ••••       |

|------------------------------------------------------------------------------------------------------------------------------|------------|

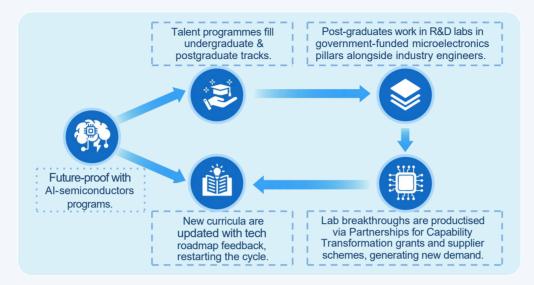

| Box 1. Singapore' s integrated semiconductor talent – innovation flywheel                                                    | 44         |

| Box 2. Global parallel – University-industry co-create and co-delivery of postgraduate programs                              | 47         |

| Box 3. China's tech talent and emergence as a global innovation superpower                                                   | 50         |

| Box 4. Global parallel – PPP for high-scale, large impact infrastructure                                                     | 55         |

|                                                                                                                              |            |

| FIGURES                                                                                                                      | ••••       |

| Figure ES-1. East Asia: Global Top 100 Science and Tech clusters                                                             | xi         |

| Figure ES-2. Semiconductor technology index by economies and foundational pillars                                            | xi         |

| Figure ES-3. A talent, R&D, and innovation flywheel                                                                          | xii        |

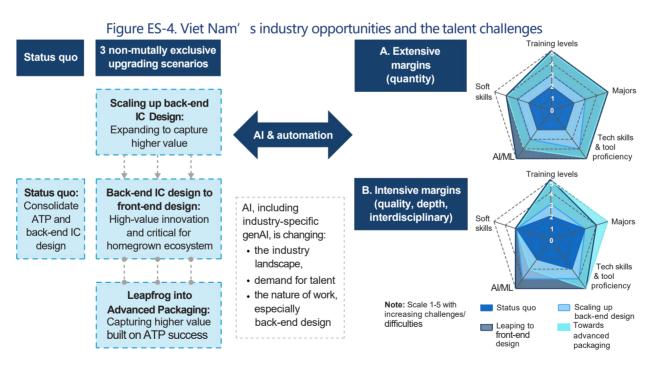

| Figure ES-4. Viet Nam's industry opportunities and the talent challenges                                                     | . xiv      |

| Figure ES-5. Aligning public and private resources for semiconductors and tech talent                                        | . xix      |

| Figure 1. Semiconductor technology index by economies and foundational pillars                                               | 2          |

| Figure 2. East Asia: Global top 100 Science and Tech clusters                                                                | 3          |

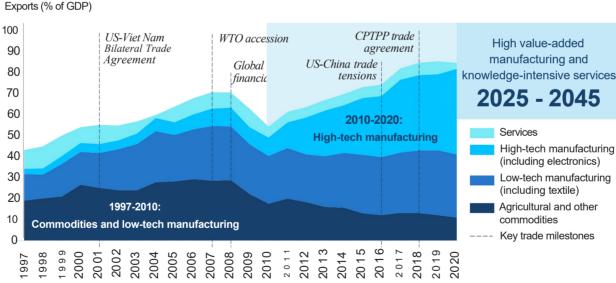

| Figure 3. An evolving export growth model to reach Viet Nam's 2045 ambitionss                                                | 5          |

| Figure 4. Innovation services productivity                                                                                   | 6          |

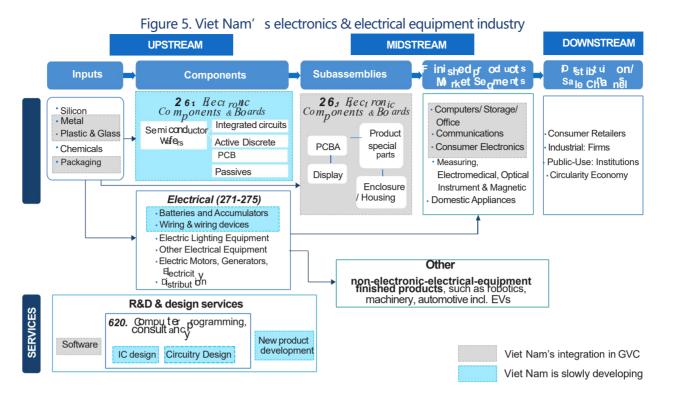

| Figure 5. Viet Nam's electronics & electrical equipment industry                                                             | 7          |

| Figure 6. Semiconductor global value chain                                                                                   | 7          |

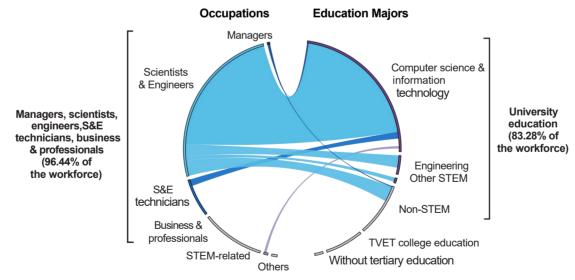

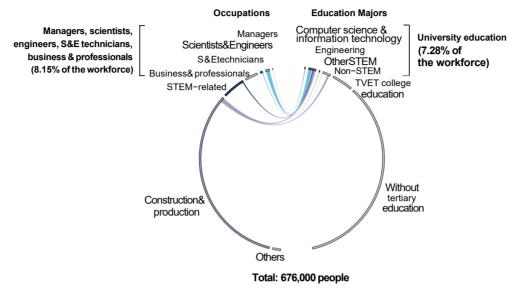

| Figure 7. Occupations and majors of the existing workforce in Computer programming services (incl. IC design firms)          | 12         |

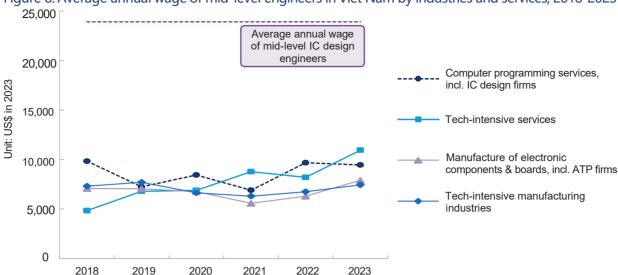

| Figure 8. Average annual wage of mid-level engineers in Viet Nam by industries and services, 2018-2023                       | 13         |

| Figure 10. Extensive and intensive margins of the talent gaps                                                                | 14         |

| Figure 9. Stock and flow of skilled workforce                                                                                | 14         |

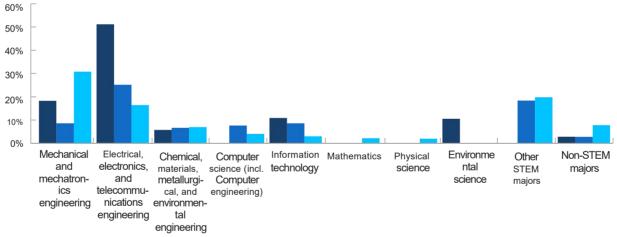

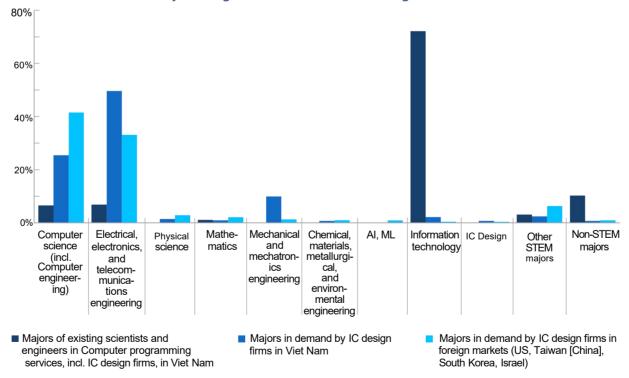

| Figure 11. Majors of existing scientists and engineers in semiconductor firms vs. current demand by firms in Viet Nam        |            |

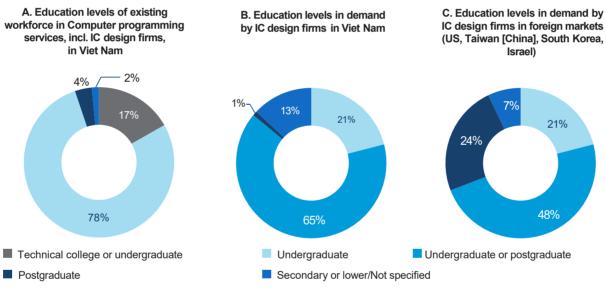

| Figure 12. Education levels of existing workforce vs. demand by IC design firms in Viet Nam and foreign markets.             | 17         |

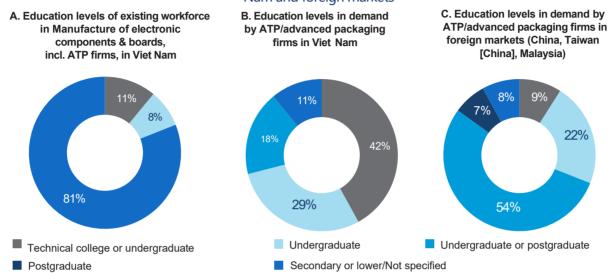

| Figure 13. Education levels of existing workforce vs. demand by ATP/advanced packaging firms in Viet Nam and foreign markets |            |

| Figure 14. Majors of existing scientists and engineers in Manufacture of electronic components & boards vs                   | j <b>.</b> |

| demand by ATP/advanced packaging firms in Viet Nam and foreign markets                                                       | . 20       |

| Figure 15. Projection of annual flow of graduates in semiconductor-related majors and their workplace                        |            |

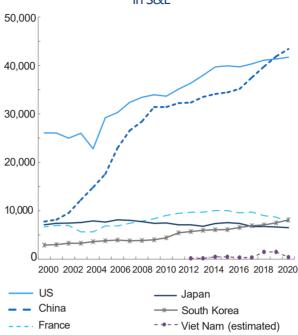

| Figure 16. Doctoral degrees awarded annually in S&E                                                                          | 26         |

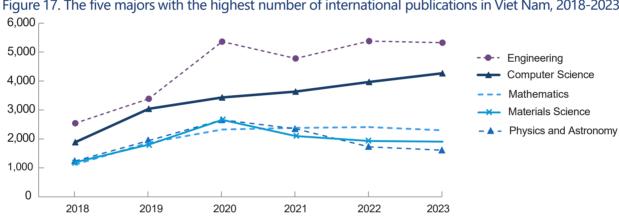

| Figure 17. The five majors with the highest number of international publications in Viet Nam, 2018-2023                      | 27         |

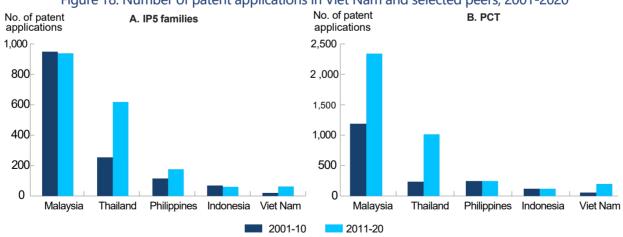

| Figure 18. Number of patent applications in Viet Nam and selected peers, 2001-2020                                           | 27         |

| Figure 19. STEM enrolment in 2023 by education majors in selected universities in Viet Nam                                   | 29         |

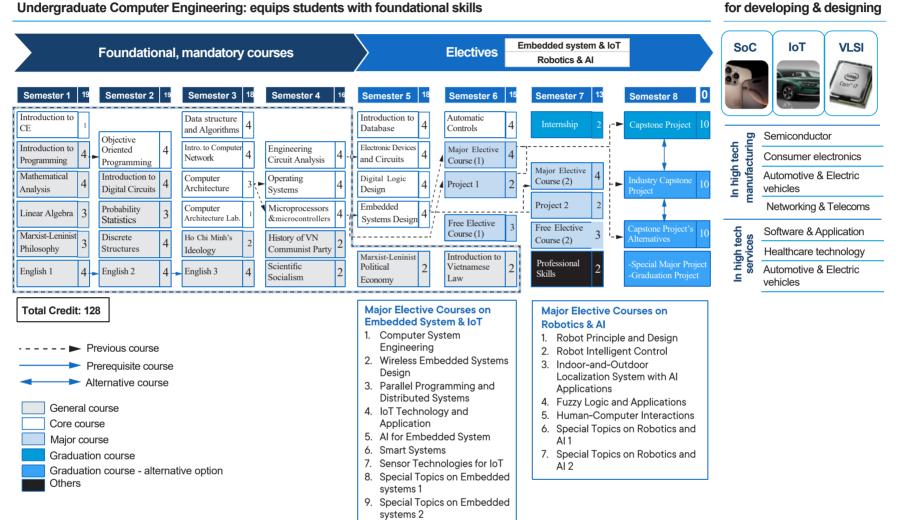

| Figure 20. Career pathway for a computer engineering graduate                                                                | 31         |

| Figure 21. A positive development at VNUHCM                                                                                  |            |

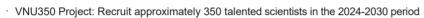

| Figure 22. Number of types of student in each research group at VNUHCM                                                       |            |

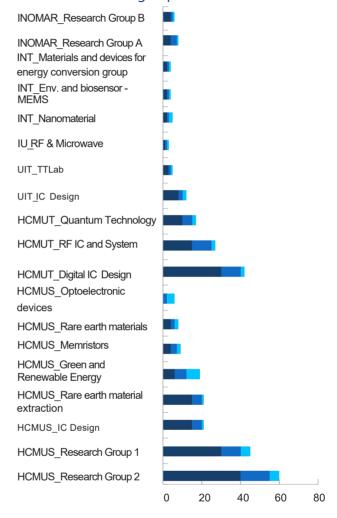

| Figure 23. External research funding from non-industry sources (US\$)                                                        | 34         |

| Figure 24. External research funding from industry sources (US\$)                                                                                 | 34    |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-------|

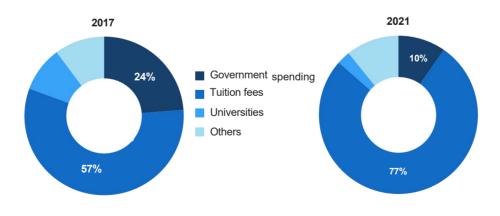

| Figure 25. Sources of university income in selected public universities in Viet Nam                                                               | 37    |

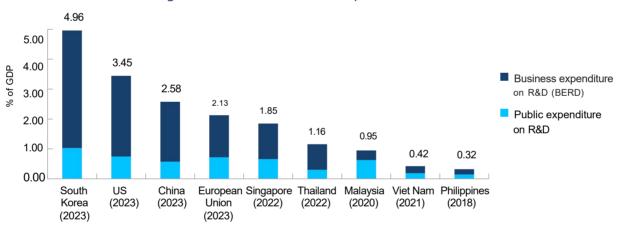

| Figure 26. Public and business expenditure on R&D                                                                                                 |       |

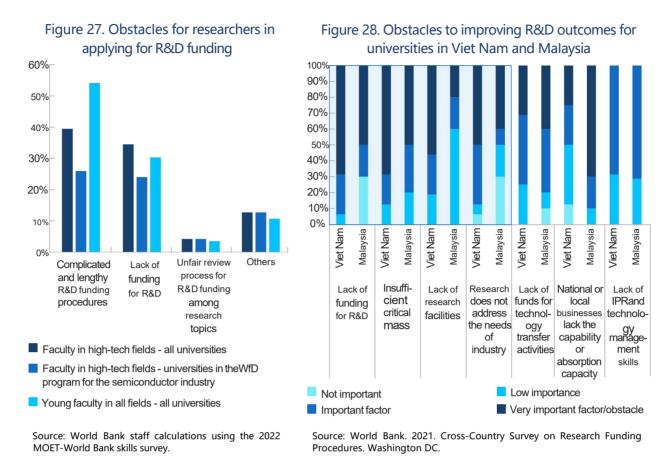

| Figure 27. Obstacles for researchers in applying for R&D funding                                                                                  | 39    |

| Figure 28. Obstacles to improving R&D outcomes for universities in Viet Nam and Malaysia                                                          | 39    |

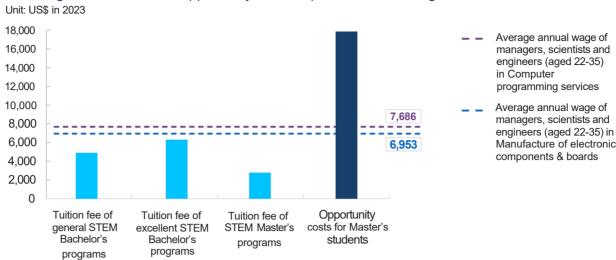

| Figure 29. Tuition and opportunity costs for potential Master degree students in Viet Nam                                                         | 46    |

| Figure 30. Financing commitment for the STI and university agenda                                                                                 | 62    |

| Figure 31. Proposed breakdown of annual expenditure, 2026-2030 (US\$ billion)                                                                     | 62    |

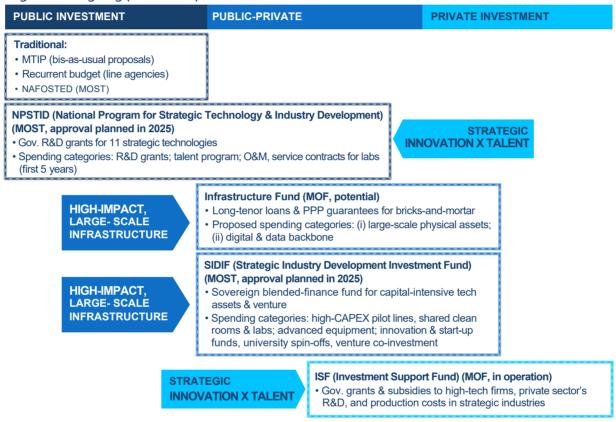

| Figure 32. Aligning public and private investment for semiconductors and tech talent and innovation                                               | 63    |

| Figure A1. Overall framework for analyzing four archetypal talent gaps                                                                            | 75    |

| Figure A2. Semiconductor firms used for talent gap analysis                                                                                       | 77    |

| Figure A3. Occupations and majors of the existing workforce in Manufacture of electronic components & boards (incl. ATP firms)                    |       |

| Figure A4. Majors of existing scientists and engineers in Computer programmingservices vs. demand by design firms in Viet Nam and foreign markets |       |

| TABLES                                                                                                                                            | ••••• |

| Table ES-1. Readiness and intensity of potential gaps for Viet Nam's semiconductor upgrade pathways                                               | xiii  |

| Table ES-2. Four intervention pillars and key implementation elements                                                                             | xvii  |

| Table 1. Global ranking of S&T clusters                                                                                                           | 3     |

| Table 2. Overview of government's financing commitment, engineering or STEM graduates, current workfin semiconductors                             |       |

| Table 3. Viet Nam's semiconductor industry: Opportunities and challenges                                                                          | 11    |

| Table 4. Demand for skills of fresh graduates with less than 2 years of experience by IC design firms                                             |       |

| Table 5. Demand for skills of fresh graduates with less than 2 years of experience by ATP/advanced packaging firms                                | 21    |

| Table 6. R&D personnel in Viet Nam, 2013-2023                                                                                                     | 26    |

| Table 7. Infrastructure needs for research labs and facilities at VNUHCM                                                                          | 35    |

| Table 8. Four intervention pillars and measures: Priority and feasibility                                                                         | 43    |

| Table 9. Ignite talent pillar: Three priority action areas and corresponding interventions                                                        | 45    |

| Table 10. Singapore's investment in high-impact infrastructure for semiconductor innovation                                                       | 54    |

| Table A1. Major East Asian S&T clusters and their academic & R&D anchors                                                                          | 71    |

| Table A2. Viet Nam's existing semiconductor workforce and expansion target                                                                        | 73    |

| Table A3. List of semiconductor firms used for talent gap analysis                                                                                | 76    |

| Table A4. Semiconductor-related service and industry and leading semiconductor firms in Viet Nam                                                  | 77    |

| Table A5. Demand for specific skills of workers with more than 2 years of experience by IC design firms                                           | 79    |

| Table A6. Demand for specific skills of workers with more than 2 years of experience by ATP/advanced packaging firms                              | 80    |

| Table A7. Three phases of developing the Viet Nam's semiconductor and electronics industries                                                      | 82    |

# Acronyms

| Al       | Artificial Intelligence                                              | HPC    | High Performance Computing                                      |

|----------|----------------------------------------------------------------------|--------|-----------------------------------------------------------------|

| ASIC     | Application-Specific Integrated Circuit                              | HUST   | Hanoi University of Science and                                 |

| AP       | Advanced Packaging                                                   |        | Technology                                                      |

| ATP      | Assembly, Testing & Packaging                                        | HVAC   | Heating, Ventilation, And Air Conditioning                      |

| AVSE     | Association of Vietnamese Scientists and                             | IC     | Integrated Circuit                                              |

| /\V3L    | Experts                                                              | ICT    | Information and Communication Technology                        |

| BiCMOS   | Bipolar Complementary Metal-Oxide<br>Semiconductor                   | INOMAR | Center for Innovative Materials and                             |

| BK21     | Brain Korea 21                                                       |        | Architectures (Vietnam National University<br>Ho Chi Minh City) |

| CAD      | Computer-Aided Design                                                | INT    | Institute for Nanotechnology (Vietnam                           |

| CMOS     | Complementary Metal-Oxide<br>Semiconductor                           | loT    | National University Ho Chi Minh City) Internet of Things        |

| CoE      | Center of Excellence                                                 | IP     | Intellectual Property                                           |

| CSE      | Computer Science Engineering                                         | IPP    | Industry Postgraduate Programme                                 |

| DFC      | Double First Class                                                   | ISF    | Investment Support Fund                                         |

| E&E      | Electronics and Electrical Equipment                                 | IT     | Information Technology                                          |

| EDA      | Electronic Design Automation                                         | ITRI   | Industrial Technology Research Institute                        |

| EDB      | Economic Development Board                                           | KAIST  | Korea Advanced Institute of Science and                         |

| EE       | Electrical Engineering                                               |        | Technology                                                      |

| ERP      | Enterprise Resource Planning                                         | KIPO   | Korean Intellectual Property Office                             |

| ESG      | Environmental, Social, and Governance                                | KPI    | Key Performance Indicator                                       |

| EU       | European Union                                                       | LDO    | Low Dropout Regulator                                           |

| EV       | Electric Vehicle                                                     | LFS    | Labor Force Survey                                              |

| FDI      | Foreign Direct Investment                                            | LLM    | Large Language Model                                            |

| FEF      | Faculty Excellence Fund                                              | MEMS   | Micro-Electro-Mechanical Systems                                |

| FPGA     | Field-Programmable Gate Array                                        | MES    | Manufacturing Execution System                                  |

| GDP      | Gross Domestic Product                                               | MIDA   | Malaysia's Industrial Development Authority                     |

| GPU      | Graphics Processing Unit                                             | ML     | Machine Learning                                                |

| GVC      | Global Value Chain                                                   | MNC    | Multinational Corporation                                       |

| HCMUS    |                                                                      | MOET   | Ministry of Education and Training                              |

| TICIVIOS | University of Science (Vietnam National University Ho Chi Minh City) | MOF    | Ministry of Finance                                             |

| HCMUT    | University of Technology (Vietnam National                           | MOIT   | Ministry of Industry and Trade                                  |

|          | University Ho Chi Minh City)                                         | MOSIS  | Metal Oxide Semiconductor                                       |

| HE       | Higher Education                                                     |        | Implementation Service                                          |

| MOST     | Ministry of Science and Technology                                 | SSIA    | Singapore Semiconductor Industry                                                          |

|----------|--------------------------------------------------------------------|---------|-------------------------------------------------------------------------------------------|

| MPW      | Multi-Project Wafer                                                |         | Association                                                                               |

| MSc      | Master of Science                                                  | STEM    | Science, Technology, Engineering, and Mathematics                                         |

| MSCA     | Marie Sklodowska-Curie Actions                                     | STI     | Science, Technology, and Innovation                                                       |

| NAFOSTED | National Foundation for Science and<br>Technology Development      | TSMC    | Taiwan Semiconductor Manufacturing<br>Company                                             |

| NIC      | National Innovation Center                                         | TSRI    | Taiwan Semiconductor Research Institute                                                   |

| NPSTID   | National Program on Strategic Technology<br>& Industry Development | TTO     | Technology Transfer Office                                                                |

| NSTIC    | National Semiconductor Translation & Innovation Centre             | TVET    | Technical and Vocational Education and<br>Training                                        |

| OECD     | Organisation for Economic Co-operation and Development             | TWAREN  | TaiWan Advanced Research and Education<br>Network                                         |

| OPEX     | Operational Expenditure                                            | UD      | University of Da Nang                                                                     |

| OSAT     | Outsourced Semiconductor Assembly and<br>Test                      | UIT     | University of Information Technology<br>(Vietnam National University Ho Chi Minh<br>City) |

| PACT     | Partnerships for Capability Transformation                         | US      | United States                                                                             |

| PCB      | Printed Circuit Board                                              | UVM     | Universal Verification Methodology                                                        |

| PCP      | Professional Conversion Program                                    | VinaREN | Viet Nam's National Research and                                                          |

| PhD      | Doctor of Philosophy                                               |         | Education Network                                                                         |

| PLL      | Phase-Locked Loop                                                  | VITALS  | Vietnam Innovation & Talent Alliance for<br>Semiconductors                                |

| PPP      | Public-Private Partnership                                         | VLSI    |                                                                                           |

| PVD      | Physical Vapor Deposition                                          | VNEI    | Very-Large-Scale Integration                                                              |

| R&D      | Research and Development                                           | VINEI   | Viet Nam Network of Higher Education<br>Innovation and Entrepreneurship Centers           |

| RF       | Radio Frequency                                                    | VNU     | Vietnam National University                                                               |

| RIE2025  | Research, Innovation, and Enterprise 2025<br>(Singapore)           | VNUHCM  | Vietnam National University Ho Chi Minh<br>City                                           |

| RTL      | Register Transfer Level                                            | VNUHN   | Vietnam National University, Hanoi                                                        |

| S&E      | Science and Engineering                                            | VSRI    | Viet Nam Semiconductor Research                                                           |

| S&T      | Science and Technology                                             |         | Institute                                                                                 |

| SCOPUS   | Elsevier's abstract and citation database                          | VUDP    | Viet Nam University Development Project                                                   |

| SgIS     | Singapore Industry Scholarship                                     | WIPO    | World Intellectual Property Organization                                                  |

| SIDIF    | Strategic Industry Development Investment                          | WLCSP   | Wafer-Level Chip Scale Packaging                                                          |

| C:D      | Fund                                                               | WB      | World Bank                                                                                |

| SiP      | System in Package                                                  |         |                                                                                           |

| SME      | Small and Medium-sized Enterprise                                  |         |                                                                                           |

| SMT      | Surface-Mount Technology                                           |         |                                                                                           |

| SoC      | System on Chip                                                     |         |                                                                                           |

# Acknowledgements

This report is a collective endeavor and involved several parts of the Bank including EDU, DD, FCI, and EAPCE, and a deliverable for the "Viet Nam' s Skilled Workforce Development for a Tech-intensive Economy" ASA.

The report was authored by Nguyet Anh Tran (Economist), Ekua Bentil (Senior Education Specialist), and Trang Hong Dao (Consultant). The following core team members co-authored background assessments, reviewed and provided substantive inputs to this report: Dung Kieu Vo (Senior Education Specialist), Huong Lan Thi Tran (Senior Digital Development Specialist), Johan Bjurman Bergman (Digital Development Specialist), Mike Nguyen (Senior Industry Consultant), Vinh Quang Dang (Senior Private Sector Specialist), Gu-Yeon Wei (Robert and Suzanne Case Professor, Harvard University), and Joshua Park (Consultant).

The report diagnosis drew significantly from the following background papers and technical notes:

- Viet Nam semiconductor industry rapid assessment, by Mike Nguyen, Huong Lan Thi Tran, and Johan Bjurman Bergman.

- 2. Skilling up for Viet Nam's semiconductor industry: Assessing talent gaps and higher education capacity, by Trang Hong Dao, Ekua Bentil, Gu-Yeon Wei, Dung Kieu Vo, Joshua Park, and NguyetAnh Tran.

- 3. Promoting university R&D and technology transfer for productivity growth in Viet Nam, by Vinh Quang Dang, Cristian Quijada Torres, Kibum Kim, NguyetAnh Tran, and Dinh Tuan Minh.

- 4. Roles of Viet Nam National University, Ho Chi Minh City in advancing Viet Nam's Semiconductor Vision: A rapid infrastructure review and policy recommendations, by Ekua Nuama Bentil, Gu-Yeon Wei, Dung Kieu Vo, and Joshua Park.

- 5. Equitable financing for Viet Nam's STEM higher education, by NguyetAnh Tran and Trang Hong Dao.

The team is grateful for valuable contributions at various stages from the World Bank and IFC colleagues: Omar Arias (Lead Economist), Diego Ambasz (Senior Economist), Mira Nahouli (Senior Operations Officer), Ridhi Gupta (Investment Officer), Abla Safir (Senior Economist), Sacha Dray (Economist), Juliana Guaqueta Ospina (Senior Education Specialist), and Dung Viet Do (Senior Country Officer).

The team greatly benefited from inputs, discussions, and reviews provided by Vietnamese university leaders and government agencies: Assoc. Prof. Vu Hai Quan (Chancellor, Viet Nam National University Ho Chi Minh City – VNUHCM), Prof. Le Quan (President, Viet Nam National University, Hanoi), Assoc. Prof. Huynh Quyet Thang (President, Hanoi University of Science and Technology), Mr. Do Tien Thinh (Deputy Director General, National Innovation Center), and from VNUHCM – Dr. Bui Thi Hong Hanh (Director of External Affairs), Assoc. Prof. Nguyen Luu Thuy Ngan (Rector, University of Information and Technology –UIT), Assoc. Prof. Pham Tran Vu (Rector, University of Technology – HCMUT), Assoc. Prof. Huynh Phu Minh Cuong (Vice Dean, UoT), and Assoc. Prof. Trinh Le Huy (UIT). The team especially thanks VNUHCM for their support in facilitating and co-organizing multiple site visits, data collection, and the report consultation workshop in VNUHCM.

We thank participants from the semiconductor industry and overseas universities for their inputsand comments, in particular, Dr. Aaron Thean (Vice President & Provost, National University of Singapore – NUS), Dr. Vu Minh Khuong (Professor, NUS), Dr. Kee-won Kwon (Professor, Sungkyunkwan University), Jeff Goss (Arizona State University), Kenneth Tse (General Director, Intel Viet Nam), Kevin Koh (President, Faraday Technology Vietnam), and Tran Dac Khoa (General Director, Renesas Design Viet Nam), and Duy Tan Tran (President, Savarti Inc.).

Financial support from Australian Aid is gratefully acknowledged for the background assessment on financing for Viet Nam's STEM higher education.

The team is grateful for the overall guidance from Mariam J. Sherman (Division Director, Viet Nam, Cambodia, and Lao PDR) and Cristian Aedo (Practice Manager, Education East Asia & Pacific). The report benefited from comments from World Bank Peer Reviewers: Alex Twinomugisha (Senior Education Specialist), Marina Bassi (Program Leader), Cristian Quijada Torres (Senior Private Sector Specialist), Hania Kronfol (Senior Digital Development Specialist), and Sandra Sargent (Senior Digital Development Specialist).

The report was assisted by Van Cam Nguyen (Program Assistant) and designed by Ha Doan (Consultant).

# Scope note

Why this report? Viet Nam has prioritized semiconductors as one of ten critical technologies and set explicit goals of becoming a global semiconductor talent hub by 2030, moving up the value chain toward higher value-added segments, and developing a complete semiconductor value chain by 2045. Delivering on that pledge hinges on strategic and urgent investment in top talent, science, and innovation.

Scope & Exclusions: This report concentrates on the most urgent gap cultivating a cadre of scientists and engineers (S&E) and, to the extent possible, tech entrepreneurs to support Viet Nam's semiconductor and high-tech ambitions. The analysis and interventions focus on the highly skilled workforce and frontier talent development, and cover research, innovation, and university-industry linkages in relation to the talent challenges.

The report recognizes that to unlock its semiconductor potential, Viet Nam must address other binding constraints, notably: weak linkages between FDI and domestic firms, emerging infrastructure gaps (e.g., energy and logistics), and intellectual property rights regulations, amid evolving geoeconomic conditions. We also acknowledge the critical role of technicians, especially those with technical degrees, in the assembly, test, and packaging segment where Viet Nam has a strong presence. However, given the scope of this report, these topics are referenced only where they directly relate to the report s focus.

#### Complementary Reports, Policy Notes and Technical Assessments

The report draws on broader World Bank research on Viet Nam's structural transformation, including Viet Nam 2045: Trading Up in a Changing World (World Bank, 2024a) the flagship report that frames value chain upgrading as a pathway to high-income status, identifies economy-wide challenges, opportunities and policy options. Improving the Performance of Higher Education in Viet Nam: Strategic Priorities and Policy Options (World Bank, 2020b) and Higher Education Financing in Viet Nam (World Bank, 2023a) provides a sectoral review of Viet Nam's higher education system.

Deep-diving assessments on key thematic areas of this report could be found in five technical and policy notes. (1) Viet Nam Semiconductor Industry Rapid Assessment (Nguyen, Tran, and Bergman, 2025) maps firm-level capabilities and market opportunities, identifying three upgrading industry opportunities across design and manufacturing. (2) Skilling up for Viet Nam's semiconductor industry (Dao et al., 2025) quantifies the demand-supply mismatches for skilled workers and higher education system capacity gaps under alternative upgrading scenarios. (3) Role of Viet Nam National University, Ho Chi Minh City in advancing Viet Nam's Semiconductor Vision (Bentil et al., 2025) deep dives into the infrastructure conditions and investment needs for training and research, and international good practices in VNUHCM. (4) Promoting University R&D and Technology Transfer for Productivity Growth in Viet Nam (Dang et al., 2025) provides a system diagnostics of university R&D and proposes legal and institutional reforms to strengthen university-led research and technology. (5) Equitable financing for Viet Nam's STEM higher education (Tran and Dao, 2025) assesses affordability and equity of STEM higher education that supports Vietnam's ambition to grow its high-tech and high value-added manufacturing base.

#### **EXECUTIVE SUMMARY**

#### A dynamic tech talent and innovation flywheel

The world is entering an artificial intelligence (AI)-driven semiconductor supercycle, with unprecedented demand for chips powering everything from generative AI to electric vehicles. Global semiconductor sales are projected to double this decade – surpassing US\$1 trillion by 2030. This AI supercycle could generate an estimated US\$15 trillion in economic output and 100 million jobs by 2030 across all sectors – if the tech infrastructure can keep up. National strength in domains such as AI and semiconductors hinges on three foundational pillars: superior innovation ecosystems, human capital, and economic resources.

Al and semiconductors are at the very core of the global technological convergence. Technology convergence is accelerating across the tech stack of five of the most critical and emerging technologies – Al, semiconductors, biotech, space, and quantum – in which advancements in one domain create network effects that spur progress in others, often in unpredictable ways.

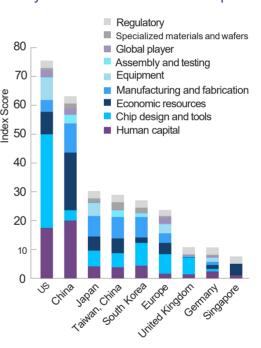

Figure ES-1. East Asia: Global Top 100 Science and Tech clusters

acceptance of such boundaries

Figure ES-2. Semiconductor technology index by economies and foundational pillars

Source: WIPO 2024

Source: Harvard's Belfer Center Critical and Emerging Technologies Index 2025 – Semiconductor Index Ranking.

Viet Nam is right at the heart of a global semiconductor cluster. Global evidence is clear: firms set up R&D-intensive activities in locations where cutting-edge talent and research co-locate with ready infrastructure. Five East Asian economies – China, South Korea, Japan, Singapore, and Taiwan (China) – rank among the global leaders in both AI and semiconductor technologies. These economies now host the world's five largest science and technology clusters and 35 of the global top 100 (with Malaysia contributing one cluster as of 2024). All of them have fused human capital development policy with long-term, aggressive investment in mission-driven research and innovation – vaulting from technology assembly and manufacturing bases to knowledge- and tech-intensive economies.

The clock for Viet Nam's talent investment is already ticking. A global semiconductor workforce shortfall – ranging from tens to hundreds of thousands in leading economies by 2030 – demonstrates that fabs and tax breaks alone cannot sustain an ecosystem. For Viet Nam, the country already possesses two critical assets: a growing tech talent pipeline and top-level political commitment. Yet, entrenched constraints in advancing the skills base, nurturing and retaining frontier talent, and building innovation capacity and infrastructure threaten to stall progress.

Figure ES-3. A talent, R&D, and innovation flywheel

This report envisions a talent, R&D, and innovation flywheel that produces a high-quality semiconductor workforce and drives innovation to realize Viet Nam's semiconductor ambitions. A successful semiconductor ecosystem rests on three foundational pillars: advanced chip design know-how, sustained capital investment, and a critical mass of highly skilled human capital – with talent development as the critical lever across all three.

This report proposes that Viet Nam must integrate its workforce development, higher education, and innovation ecosystems so that the government, universities, and industry can reinforce each other in cultivating a deep, expansive talent pool, driving research and innovation, and propelling the country up the value chain – for the semiconductor and other technology-intensive industries.

To act with speed and scale, four mutually reinforcing pillars are proposed:

- Ignite Talent expand and deepen the skilled workforce, and nurture a frontier tech talent pipeline.

- 2. Build Shared Training and R&D Infrastructure give students and universities access to industry-standard tools, facilities and infrastructure.

- Catalyze University-Industry Innovation turn research into marketable designs, products and solutions.

- 4. Govern & Finance for Results lock in accountability and sustained funding.

Investing in tech talent can pay economy-wide dividends – creating tens of thousands of high-paying jobs and boosting other high-tech sectors. A larger, more skilled workforce also enables local firms to move up the value chain and attracts higher-quality foreign direct investment (FDI), creating a virtuous cycle. Lastly, breakthroughs in chips generate network effects, catalyzing progress in strategic technologies such as AI, biotech, and space. The milestones are clear. By 2035, Viet Nam should aim to be recognized as a global semiconductor talent hub – with a self-sustaining pipeline, vibrant domestic chip design houses, and the credibility to attract the next wave of investment.

The window to deliver these outcomes is narrow - but still open. Regional peers and aspirants such as Malaysia, Singapore, and China are already expanding rapidly in cutting-edge semiconductor areas. Viet Nam urgently needs to address its talent shortfall in order to compete. While such bold actions present challenges, these can be effectively mitigated. Acting decisively now will determine whether Viet Nam shapes – or merely observes – the future of advanced industry in the region.

No country has ever suffered from having "too many" quality talent - but many have lost out by having too few.

#### Viet Nam's semiconductor moment: Moving up the ladder

A confluence of factors makes Viet Nam's ambitious semiconductor vision timely: its young and technically skilled workforce, the government's prioritization of innovation, and mounting interest from global tech firms. Many of these firms are already present or expanding in Viet Nam, drawn by an enabling environment primed for innovation-led growth – thanks to a suite of new supportive laws and funding programs.

Table ES-1. Readiness and intensity of potential gaps for Viet Nam's semiconductor upgrade pathways

| Industry window                                | Viet Nam<br>readiness 2024* | Knowledge /<br>Talent intensity | Technology<br>intensity | Capital intensity |

|------------------------------------------------|-----------------------------|---------------------------------|-------------------------|-------------------|

| Consolidate assembly, testing & packaging base | •••• (4/5)                  | • • • • (1/5)                   | • • • (1/5)             | ●●●○ (3/5)        |

| Expand back-end design services                | ••○○ (2/5)                  | ●●●○ (3/5)                      | ●●●○ (3/5)              | • · · · · (1/5)   |

| Move into front-end IC design                  | • 000 (1/5)                 | ●●●● (5/5) ★                    | ●●●● (5/5)★             | ●●●● (4/5) ★      |

| Leapfrog to advanced packaging                 | • · · · · (1/5)             | •••• (4/5)                      | ●●●● (4/5)              | ••••• (5/5) ★     |

\* Viet Nam readiness 2024: composite score for current workforce, R&D capability and industrial base.

📺 High fiscal-risk cells – large public funding requirement; PPPs or risk-sharing mechanisms recommended.

Viet Nam can pursue three strategic upgrade pathways, building on its existing strengths in back-end manufacturing (ATP – Assembly, Testing, Packaging) and growing capacity in back-end design services:

- Expand back-end design services: Viet Nam can grow as a hub for outsourced back-end design, particularly in layout and verification services. The number of IC design houses (around 40 today) could potentially double within five years, creating thousands of new engineering jobs. This segment has moderate knowledge intensity and can scale relatively quickly if the right skills are developed.

- Move into advanced packaging: Viet Nam could leapfrog into advanced packaging (e.g., 2.5D/3D chip stacking and System-in-Package (SiP) technologies) by leveraging early investments. Intel Viet Nam's pilot 3D packaging line and Amkor's new SiP facility already give Viet Nam a first-mover edge in the region. Advanced packaging is both technology- and capital-intensive, but it could become a niche specialization in which Viet Nam stands out.

- Leapfrog to front-end design: Developing indigenous chip intellectual property (IP) and full systemon-chip products would yield high-value design jobs and royalty streams. This path is highly knowledgeintensive, requiring top engineering and science talent (often with postgraduate degrees) to design and architect complex chips.

These three upgrading "windows" are mutually reinforcing, not mutually exclusive. Expanding Viet Nam's already solid foothold in back-end manufacturing, for example, could generate large-scale employment and industrial capability – thereby enabling a transition to higher-value segments like advanced packaging.

At the same time, Viet Nam also needs to consolidate its existing base in ATP. The country already has a solid foothold in back-end manufacturing with large investors like Intel and Amkor. Expanding existing plants and attracting new ones could add tens of thousands of skilled jobs by 2030, anchoring a local supply chain. Equally important, a strong ATP base generates large-scale employment and builds essential industrial knowhow, which serves as a springboard to higher-value activities such as advanced packaging.

The connecting factor in all these cases is talent, R&D, and innovation: the more Viet Nam can acquire and develop talent, the greater its agility across the semiconductor value chain.

#### Semiconductor talent challenges: Extensive, intensive, and integrative margins

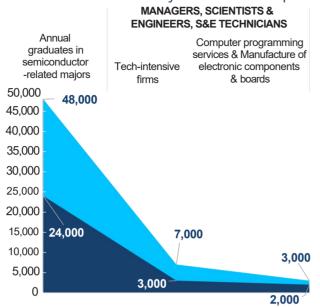

Positives regarding Viet Nam's talent pool certainly exist. Enrollments in science and engineering fields are rising by about 9 percent annually, for instance. Its top universities are also gaining regional recognition in the fields of science, technology, engineering, and mathematics (STEM). Currently, the country has over 500,000 professionals in their twenties and thirties with STEM degrees, with a further 24,000 projected to join the workforce each year.

If Viet Nam's semiconductor aspirations are translated into concrete actions that address identified gaps, it will vastly increase talent needs on:

- Extensive margins quantity of skilled workers and frontier tech talent;

- Intensive margins quality, depth, and interdisciplinarity, and with future-proof skill sets;

- Integrative margins training-to-work, lab-to-fab, R&D-integrated training.

Future-Proof: Compounding the challenge is the fast-evolving nature of Al and interlocked technologies. Al is reshaping the industry, with the race for more powerful Al capabilities driving demand for advanced chips. It is also transforming the nature of demand for skills and intensifying the talent challenge. Alpowered design tools, for example, are automating certain routine chip design tasks and may reduce the need for entry-level back-end designers. At the same time, Al is increasing demand for engineers with expertise in cutting-edge areas such as machine learning and data science, and with the ability to solve complex edge-case problems.

Quantity: Viet Nams talent pool currently lacks what it needs to succeed in its semiconductor industry upgrade. In the country's strong assembly and testing segment, for example, only around 8 percent of workers in electronics factories hold a university degree; yet nearly half of current job postings in that segment require a bachelor's degree or higher. Scaling up back-end chip design activities would require tens of thousands of additional engineers beyond the current supply.

Quality & Depth: Moving into front-end design requires computer architects, chip designers, and other kinds of specialists with advanced degrees. Such talent is extremely scarce in Viet Nam; only around 4 percent of the current semiconductor workforce has a postgraduate degree, compared to around 30 percent in leading hubs. Advanced packaging operations present the same dilemma, with rising demand for expertise in materials science, chemistry, physics, and reliability engineering.

Integration: Meeting the fast-evolving technology cycles of the semiconductor industry is not just a question of improving skills in the abstract. To remain relevant and innovative, specialists must be tapped into the latest market trends and developments. At present, talent development takes place too far from the industry frontline. Breaking down existing silos between the education sector and business is therefore essential.

The multifold challenges of quantity, quality and depth, and integration in talent development underscore the urgency of immediate action. Viet Nam cannot rely on incremental improvements while others are already making bold, decisive moves.

#### Five critical decisions for 2025

Viet Nam has articulated a bold vision; 2025 is the year to pivot from planning to action. To kick-start the talent drive, five critical decisions are recommended for immediate implementation. Each decision is achievable within a year and aligns with the long-term pillars of the semiconductor ecosystem namely, human capital, technology, and investment.

- Decision 1: Fast-track a Semiconductor Graduate Fellowship (M.Sc./Ph.D.) Program. A national "Semiconductor Fellowship" program would fund full graduate scholarships for talented students to attend top-tier programs (abroad or in Viet Nam), creating a pipeline of tech talent and future faculty. Fellows would be bonded to return and work in Viet Nam through binding agreements and incentives.

- 2025 action: Secure dedicated funding and launch the call for applications for the first cohort of fully funded semiconductor M.Sc./Ph.D. scholarships.

- Decision 2: Launch a "Faculty Excellence Fund." Establish a competitive program to build up Viet Nam's teaching and research faculty in critical semiconductor-related disciplines by: sponsoring early-career Vietnamese lecturers to pursue PhDs or postdoctoral training abroad; attracting top Vietnamese diaspora or foreign experts to teach in Viet Nam; and providing grants for lab setup and research upon their return.

- 2025 action: Allocate funding starting in 2025 to support at least 50+ new faculty PhD scholarships (domestic or overseas) and initiate the hiring of 40+ international experts in key fields into universities.

- Decision 3: Create a national "EDA Cloud" platform. Provide centralized, low-cost access to industry-standard chip design software (Electronic Design Automation, or EDA, tools) for universities, research institutes, and start-ups. A government-backed EDA platform would negotiate bulk licenses and host these tools for shared use.

2025 action: Procure bulk EDA software licenses and establish an operational EDA Cloud platform by end-2025.

- Decision 4: Co-fund semiconductor training centers and labs. Jump-start infrastructure investment for talent development by co-investing in national semiconductor training and R&D hubs. Through public—private partnerships (PPPs), the government would match funding (e.g., 50–60%) for critical facilities, with industry contributing the remainder along with operational expertise.

- 2025 action: Commit funding in 2025 for at least three national semiconductor hubs, and kick-start two pilot projects (e.g., a training fab and an advanced packaging center) within the year.

- Decision 5: Establish a Semiconductor & Tech Talent Governing Body. Form a high-level talent governing body comprising representatives from government, industry, and academia to coordinate the national talent agenda, with the goal of aligning efforts and driving public–private partnerships.

- 2025 action: Officially launch the governing body by 2025 to signal whole-of-government commitment.

Collectively, such moves would give a huge boost to Viet Nam's talent engine and send a powerful signal to investors – and to the country's talent – that the country "means business" in semiconductors.

#### An integrated roadmap to 2035: Objectives and proposals

Important as quick wins are, Viet Nam's semiconductor ambitions also require sustained effort through 2030 and beyond. This is best achieved through an integrated roadmap to 2035, aligned with the country's broader industry development timeline. The proposed roadmap is built on existing government commitments – such as the initial 2030 targets and the existing policy landscape – as a foundation.

Underlying these proposals are the following principles:

- Close today's gaps and pre-empt tomorrow's: Every action is chosen because it tackles current skills shortages while anticipating future gaps as Viet Nam climbs the value chain.

- Build a full talent pipeline stock and flow: These measures strengthen the stock of existing scientists, engineers, and technicians, while enlarging the flow of pnew graduates and upskilled workers.

- Act on three margins of scarcity: Interventions boost the extensive margin (quantity of qualified talent), the intensive margin (depth of specialization, interdisciplinarity, frontier knowledge and skills), and the integrative margin (training-to-work, lab-to-fab, R&D-integrated training).

- Sequence "quick wins" with long-term gains: Early, visible results (e.g., bootcamps, shared EDA licenses) build momentum while laying foundations (e.g., cleanrooms, PhD pipelines) for the 2035 horizon.

- Augment, be adaptable, and scalable for a broader "Strategic Tech" agenda: The recommendations are semiconductor-centric today, but every instrument can later scale to support other strategic technologies.

Key proposals, summarized in Table ES-2, ensure that higher education institutions, research institutes, and industry can effectively collaborate and innovate. They address key opportunities and current gaps resulting in the talent challenges, including faculty shortages and retention challenges, underdeveloped postgraduate programs, teaching and research infrastructure shortfalls, fragmented industry-university engagements, low innovation and entrepreneurial outputs, and nascent Al integration in training programs and research.

Table ES-2. Four intervention pillars and key implementation elements

|        | INTERVENTION PROPOSALS                                                                                                                                                                                                                                                                                                                                          | TIME<br>HORIZON* |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| PILLAR | 1: IGNITE TALENT                                                                                                                                                                                                                                                                                                                                                |                  |

| 1      | Semiconductor Fellowship Program (postgraduate): i) MSc/PhD scholarships to study in leading institutions in Viet Nam or abroad; ii) mix of domestic and overseas "twinning" degrees; iii) bonding agreements to work in Viet Nam.                                                                                                                              | ST / MT          |

| 2      | Advanced upskilling & professional conversion: i) 3-6-month bootcamps run by National Innovation Center, anchor universities, and firms; ii) vendor academies by leading firms; iii) Professional Conversion Program for mid-career engineers from adjacent sectors; iv) Multinational (MNC) firms-led on-the-job upskilling with strong government incentives. | ST               |

| 3      | Faculty Excellence Fund / Program: i) fully-funded PhDs abroad for young lecturers with return grants; ii) visiting-professor & diaspora tracks; iii) performance incentives for research and curriculum upgrades; iv) sabbaticals in industry.                                                                                                                 | ST / MT          |

| 4      | Semiconductor Faculty Fellowship (nucleus leaders): competitive grants to create specialized labs, covering equipment and PhD students.                                                                                                                                                                                                                         | MT/ LT           |

| 5      | Industry experience – internship & apprenticeship: i) paid internship and apprenticeship in firms or labs with stipends subsidised by Investment Support Fund (potentially).                                                                                                                                                                                    | ST               |

| 6      | Industry-linked curriculum reforms: i) joint Academic & Industry Advisory Boards update reference curricula annually; ii) embed Electronic Design Automation (EDA) tool certification, AI-hardware and supply-chain modules; iii) shared courses and training programs across leading universities.                                                             | ST               |

| PILLAR | 2 – BUILD SHARED R&D INFRASTRUCTURE                                                                                                                                                                                                                                                                                                                             |                  |

| 7      | National IC Design & Prototyping "Commons": central Electronics Design Automation (EDA) license library; High performance computer (HPC), IP core repository and Multiproject wafer (MPW) shuttle services hosted by national hubs/centers, open to universities and startups.                                                                                  | MT               |

| 8      | University Lab Upgrade Program: competitive US\$5-10 m grants to 5-10 universities to upgrade university training labs, including operation and maintenance budget and technician training.                                                                                                                                                                     | ST               |

| 9      | Pilot Advanced Packaging & Testing Facility: shared 2.5D/3D pilot line jointly funded and established in partnership with the industry; integration of workforce training and translational R&D feasibility study completed by 2026.                                                                                                                            | MT               |

| 10     | Public-Private Partnerships (PPPs) for large-scale infrastructure: full-scale national semiconductor and high tech hubs (for interlocked critical and emerging technologies), financed with 50:50 private-public split; 10-15 percent of capex reserved as maintenance endowment.                                                                               | MT / LT          |

| PILLAR | 3 – CATALYSE UNIVERSITY–INDUSTRY–GOVERNMENT INNOVATION                                                                                                                                                                                                                                                                                                          |                  |

| 11     | Matching-grant consortia for R&D: Semiconductor Innovation Challenge funds joint university-industry projects on a 50/50 cost share; pilot call 2025-26 with international expert panel.                                                                                                                                                                        | ST               |

| 12     | Technology-transfer offices, commercialisation funds & start-up vouchers: strengthen university Technology Transfer Office, provide proof-of-concept grants, and issue startup vouchers to spinoffs.                                                                                                                                                            | ST / MT          |

| 13       | VITALS program & pilot-line innovation hubs: a full scale program co-fund linking universities with industry and local firms with MNCs for knowledge and technology spillovers; upskilling, expanding advanced packaging and pilot lines, and track spillover (Pillar II-9 and II-10).                             |    |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| PILLAR 4 | 4 - GOVERN & FINANCE FOR RESULTS                                                                                                                                                                                                                                                                                   |    |

| 14       | Semiconductor and Tech Talent governing body: i) an apex steering body under the National Science, Technology, Innovation and Digital Transformation Steering Committee; includes ministries, universities and industry; ii) a coordinating agency for unified action plan, implementation, and progress tracking. | ST |

| 15       | One-stop financing platform: digital portal/platforms pooling multiple available funding sources; single call for integrated talent-and-innovation proposals; dynamic public private matching ratios.                                                                                                              | ST |

\*Note: Time horizon is indicative of the implementation start of the proposal. Short term (ST) refers to approximately 1-2 years (2025-2026), medium term (MT) 3-5 years (2027-2030), long term (LT) beyond 5 years (2031-2035), from 2025.

#### **Risks & mitigation**

No ambitious program is risk-free. Viet Nam's semiconductor talent initiative faces four main risks, all of which can be mitigated with sufficient foresight:

Risk 1: Brain drain: After advanced training (especially abroad), some individuals may choose to leave Viet Nam for higher-paying opportunities, undercutting the local talent pool.

Mitigations: Implement bonding agreements for scholarship recipients. Simultaneously, improve local incentives to return by creating attractive R&D roles and career pathways in Viet Nam. Also, engage overseas Vietnamese experts in domestic projects, creating a "brain circulation".

Risk 2: Fiscal stress: The program's sizable public funding (about \$2 billion over 2026–2030) could face shortfalls if economic conditions change or government priorities shift.

Mitigations: Prioritize the initiative as a national priority with multi-year budget earmarks to protect and sustain funding. Phase the project into scalable segments to ensure core elements (scholarships, critical labs) are funded first if budgets tighten. Embed private co-financing and pursue alternative funding sources (e.g., industry contributions, donor support). Demonstrate early successes to sustain political support.

Risk 3: Demand volatility: A global downturn could see chip demand fall or a new disruptive technology could temporarily alter labor demands.

Mitigations: Design curricula and training with flexibility and breadth. Emphasize fundamental skills (e.g., solid electronics engineering, programming, problem-solving) that transcend industry cycles. Future proof talent programs through continuous updates. Avoid narrow over-specialization, maintain an agile training and workforce development system and a culture of life long learning.

Risk 4: Private-sector participation: Private-sector actors may fail to co-invest or engage to the extent expected, due to lack of awareness, mistrust, or their own constraints.

Mitigations: Socialize the program and its incentives through the Talent Council and industry associations. Simplify processes for firms to engage (e.g., easy applications for matching grants). Highlight quick wins to build momentum.

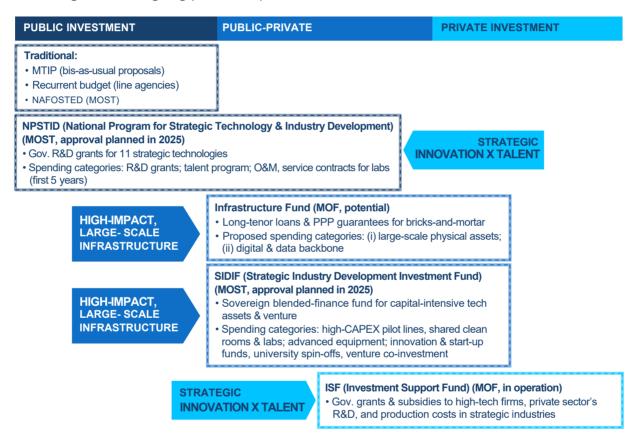

#### Jobs upside vs fiscal cost

Manageable expenditure: Investing in semiconductor talent will require substantial funding, but the growth dividend it will yield far outweighs the cost. The total program is estimated to need about \$2 billion over 2026–2030 (combined public and private investment). This is roughly 0.1–0.2% of Viet Nam's GDP per year – a manageable sum considering the strategic importance of semiconductors and the expected returns. With public debt relatively low, Viet Nam has the fiscal space to act now.

Return on investment: In return for this investment, Viet Nam stands to gain a vibrant high-tech industry generating thousands of well-paid jobs, greater domestic value-add (reducing reliance on imported hightech inputs), and economy-wide productivity gains from technology diffusion. Budget outlays on scholarships, faculty, and labs should primarily be viewed as investment in future growth, not mere expenditures.

Figure ES-5. Aligning public and private resources for semiconductors and tech talent

#### **Bottom line**

Semiconductor and tech talent is the make-or-break factor for Viet Nam's high-tech ambitions. Unlike low-cost labor in apparel or assembly – where Viet Nam has excelled – the semiconductor industry demands deep skills and continuous innovation. Against this once-in-a-generation landscape of opportunities, a lingering question sometimes arises: could Viet Nam produce "too many" STEM graduates, too quickly? Global evidence - and Viet Nam' s own experience - suggests the opposite - a greater risk is having too few. At every juncture when Viet Nam has raised its high-tech ambitions, the real bottleneck has been a shortage of engineers and scientists – never an excess.

# PART I. THE CASE FOR ACTION: INVESTING IN THE BRAIN OF THE "BRAINS"

# 1. VIET NAM' S SEMICONDUCTOR MOMENT: MOVING UP THE VALUE LADDER

#### 1.1. Semiconductors, AI, technology convergence, and the tech talent race

The world is entering an artificial intelligence (AI)-driven semiconductor supercycle, with unprecedented demand for chips powering everything from generative AI to electric vehicles (EVs). Global semiconductor sales are projected to double this decade – surpassing US\$1 trillion by 2030 – fueled largely by AI, data centers, EVs, and Internet of Things (IoT) adoption. The rise of generative AI models in 2023, for example, triggered a rush for advanced AI accelerators (graphics processing units – GPUs), causing supply bottlenecks and soaring prices. This AI supercycle could generate an estimated US\$15 trillion in economic output and 100 million jobs by 2030 across all sectors – if the tech infrastructure can keep up. National strength in domains like AI and semiconductors hinges on superior innovation ecosystems, human capital, and economic resources (Rosenbach et al., 2025).

Al and semiconductors are at the very core of global technological convergence. Technology convergence is accelerating across the tech stack of five of the most critical and emerging technologies – Al, semiconductors, biotech, space, and quantum – in which advancements in one technology create network effects that spur progress in others, often in unpredictable ways (Park, 2019; Rosenbach et al., 2025; Anil, 2025). Powerful Al models are already accelerating chip design and drug discovery, while advances in quantum research are opening new frontiers in semiconductor materials, particularly for next-generation and quantum computing applications.

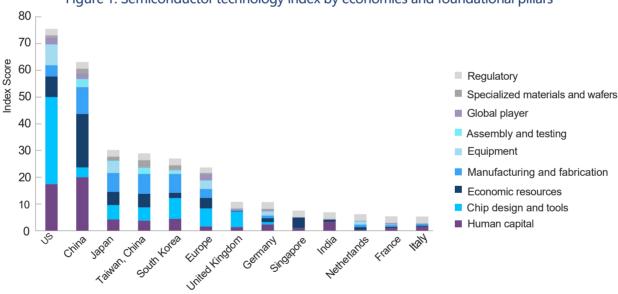

Figure 1. Semiconductor technology index by economies and foundational pillars

Source: The Harvard's Belfer Center Critical and Emerging Technologies Index, Defense, Emerging Technology, and Strategy (DETS) Program (accessed on June 22, 2025).

Note: The index is calculated by assigning different weights to key dimensions (or pillars) based on their relative importance. Three top pillars for semiconductors technology are: (i) Chip design and tools (weighted at 32.5%) captures a nation's ability to architect and define next-generation chips; (ii) Human capital (weighted at 30%) captures the depth and quality of a nation's semiconductor talent pool; (iii) Economic resources (weighted 20%) captures the financial resources of a nation available to its semiconductor ecosystem.

<sup>&</sup>lt;sup>01</sup> Burkacky, O., Dragon, J., & Lehmann, N. (2022, April 1). The semiconductor decade: A trillion-dollar industry. McKinsey & Company. Retrieved from https://www.mckinsey.com/industries/semiconductors/our-insights/the-semiconductor-decade-a-trillion-dollar-industry

Semiconductors are the "brains" behind all modern technologies—from Al and digital transformation to frontier breakthroughs—while talent is the "brain" behind the chip itself. The bedrock of semiconductors, as a critical technology and industry ecosystem, is founded on technology (chip design and tools), human capital (specialized workforce and science, research and development (R&D) talent), and capital (economic resources) (Rosenbach et al., 2025; BCG, 2022; SIA & BCG, 2020; SIA & BCG, 2021). Five East Asia economies China, South Korea, Japan, Singapore, and Taiwan (China) rank atthe global top for both Al and semiconductor technologies (Figure 1). Massive science, technology, engineering, and mathematics (STEM) graduate outputs, deep engineering talent pools, and robust researcher pipelines power these strong East Asian innovation ecosystems. For example, Singapore's semiconductor strategy leans on its highly skilled workforce, the talent-innovation flywheel, modern infrastructure, and strong ecosystem linkages, to move from electronics manufacturing into chip design and advanced packaging.

The East Asian economies in the global top 10 positions for semiconductors technology also host 36 of the global top 100 science and tech (S&T) clusters according to the Global Innovation Index 2024.<sup>92</sup> All the world's five biggest S&T clusters are now located in East Asia, and in the top 100 there are 26 clusters in China, four in South Korea, three in Japan, and one each in Malaysia, Taiwan (China), and Singapore (Figure 2, Table 1). One common feature of these S&T clusters is that they always coalesce around flagship research universities with the latter acting as the anchor for talent, basic research, and spin-off activity (See more in Annex 2). For example, inChina s two biggest hubs Shenzhen Hong Kong Guangzhou and Beijing Shenzhen University, the Hong Kong universities, and SUSTech in the Pearl River Delta, together with Tsinghua and Peking University in the capital, supply the bulk of the region's graduate engineers and host joint labs with firms such as Huawei, CATL, and SMIC. South Korea's four WIPO-listed clusters are likewise university-centered with Seoul Incheon around Seoul National University and the "Techno Valley" of Yonsei and Korea University.

Figure 2. East Asia: Global top 100 Science and Tech clusters

Table 1. Global ranking of S&T clusters

| Number of S&T clusters in the global top 100 in 2024 |           |           |           |            |

|------------------------------------------------------|-----------|-----------|-----------|------------|

|                                                      | Top<br>10 | Top<br>20 | Top<br>50 | Top<br>100 |

| US                                                   | 3         | 6         | 11        | 20         |

| China                                                | 4         | 8         | 15        | 26         |

| Taiwan,<br>China                                     | 0         | 0         | 1         | 1          |

| South<br>Korea                                       | 1         | 2         | 2         | 4          |

| Japan                                                | 2         | 3         | 3         | 3          |

| Singapore                                            | 0         | 0         | 1         | 1          |

| Malaysia                                             | 0         | 0         | 0         | 1          |

The boundaries, colors, denominations and other information shown on any map in this work do not imply anyjudgement on the part of The World Bank concerning the legal status of any territory or the endorsement or acceptance of such boundaries.

Source for Figure 2 and Table 1: WIPO - Global rankings of science and technology clusters, 2024.

Note: Clusters are defined as geographical areas that show a high density of inventors and scientific authors. Two innovation metrics are used to construct the top 100 S&T clusters worldwide are location of inventors listed on published patent applications and authors listed on published scientific articles.

wipo (2024). Global Innovation Index 2024: Science and Technology Cluster Ranking. Retrieved at https://www.wipo.int/en/web/global-innovation-index/2024/science-technology-clusters

Table 2. Overview of government's financing commitment, engineering or STEM graduates, current workforce in semiconductors

| Country                      | Government's committed budget (selected, not exhaustive information)                                                           |                                                                                                                                                                 |                                                                                    | Annual<br>engineering/                                                      | Semiconductor current                                       |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------|

|                              | Industry/ ecosystem                                                                                                            | R&D & innovation                                                                                                                                                | Workforce<br>development                                                           | STEM university<br>graduates                                                | workforce                                                   |

| Viet Nam <sup>03</sup>       |                                                                                                                                |                                                                                                                                                                 | US\$1.08 bil. for<br>semiconductor<br>(2025-2030) (not<br>yet appropriated)        | 148,000 (2023)                                                              | Approximately<br>15,000 – 17,000<br>(2025)<br>(See Annex 3) |

| China <sup>04</sup>          | >US\$50 bil. via China<br>IC Industry Investment<br>Fund (since 2014)                                                          |                                                                                                                                                                 |                                                                                    | 1.9 mil. (2022),<br>including 170,000<br>in microelectronics<br>(2022)      | 570,000 (2022)                                              |

| Singapore <sup>05</sup>      |                                                                                                                                | US\$18.8 bil. for<br>R&D (2021-2025)<br>via RIE2025 (4<br>microelectronics<br>pillars);<br>US\$748 mil.<br>for biotech &<br>semiconductor<br>R&D infrastructure | US\$75 mil. for internships & traineeships                                         | 7,000 university<br>STEM graduates;<br>2,500 polytechnic<br>diplomas (2022) | 35,000 (2023)                                               |

| South<br>Korea <sub>06</sub> | US\$246 bn for the Yong<br>Mega-Cluster (2023-204<br>six advanced fabs plus 2<br>fabless firms; designated<br>complex in 2024. | 42). Project covers<br>200+ supplier &                                                                                                                          | US\$1.2 bil. for<br>K-Semiconductor<br>Strategy 2021-2030                          | 130,000 (2020)                                                              | 180,000 (2021)                                              |

| Malaysia <sup>07</sup>       |                                                                                                                                |                                                                                                                                                                 | US\$5 bil.<br>for 60,000<br>semiconductor<br>engineers                             | 50,000 (2018) with<br>10,000 engineers;<br>15,000 technicians               | 105,000 (2019)                                              |